Tesla CEO Elon Musk outlined Tesla’s self-developed chip plans yesterday after announcing the tape-out of the AI5 chip.

Musk stated that the effective computing power of an AI5 chip is five times that of a dual-chip AI4 solution. The subsequent AI6 chip will be manufactured by Samsung Electronics’ foundry business at its Taylor, Texas fab using a 2nm process, equipped with LPDDR6 memory, achieving double the performance in a similar area (400+ mm²). The AI6.5 chip will be manufactured by TSMC Arizona, a US subsidiary of TSMC, using a 2nm process, further enhancing performance.

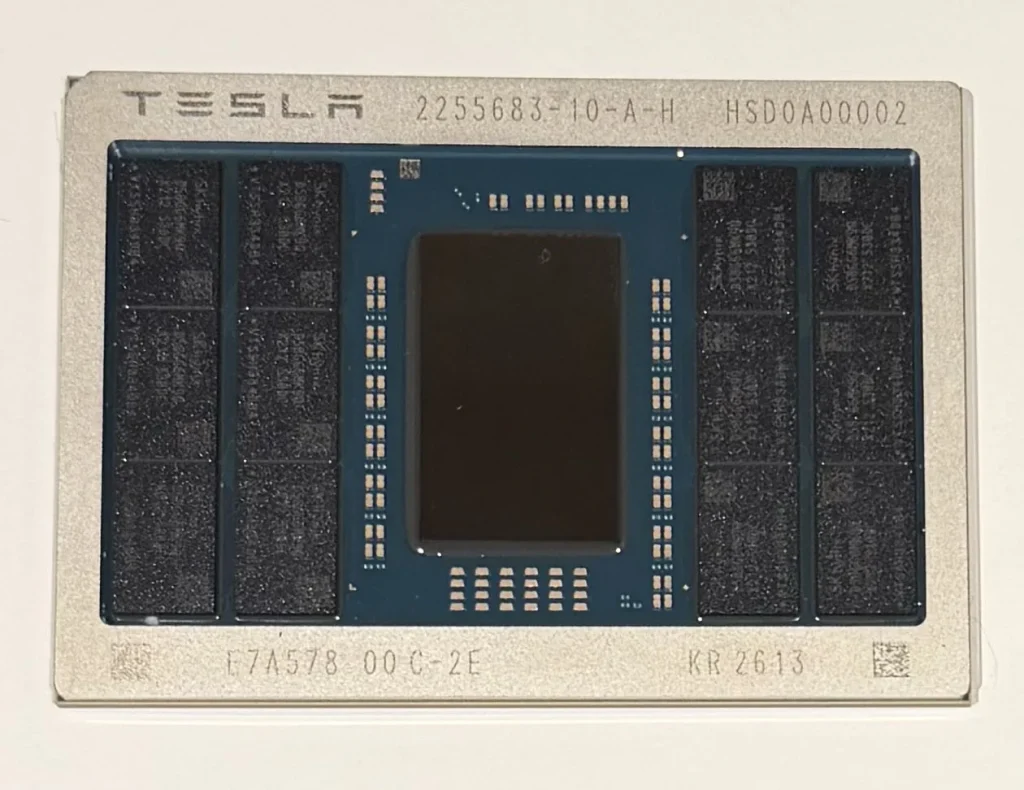

AI5

In terms of chip design, both AI6 and AI6.5 will have approximately half of their TRIP AI computing accelerators tightly integrated with SRAM, significantly improving effective bandwidth.

The AI5 chip has a significant difference in length and width between the memory chips packaged on both sides, which does not conform to the characteristics of GDDR series chips, and is likely to be LPDDR5X; it is only natural that AI6 will be upgraded to LPDDR6.